## **RECAP**

Adrian Jackson adrianj@epcc.ed.ac.uk

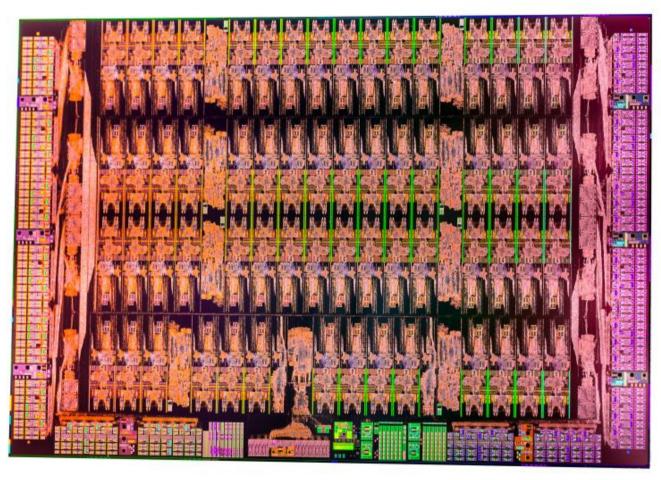

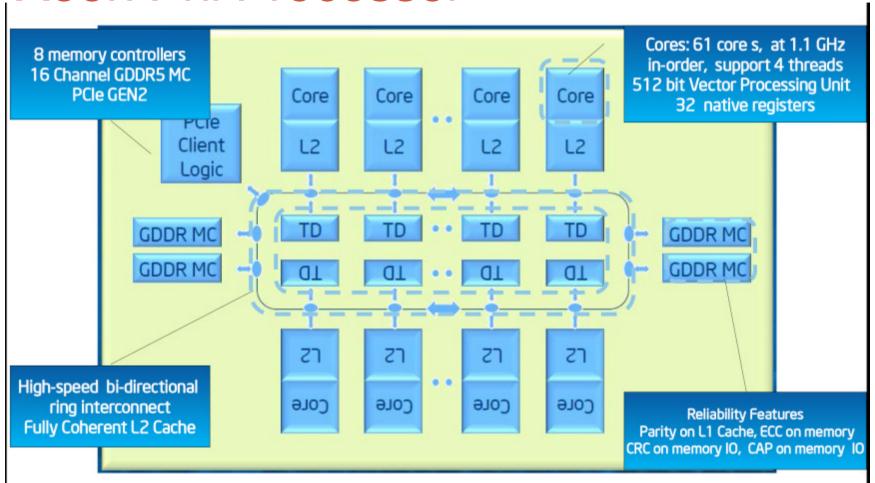

# Xeon Phi Processor

### Xeon Phi Processor

#### Xeon Phi

- 60 cores -> 240 threads

- 120 or above required for instruction issuing

- Two different programming models

- Offload, native

- OpenMP and MPI (also Cilk, OpenCL)

- Also can use libraries to do the same (i.e. MKL)

- Accelerator card

- Same as GPU, restrict data transfers for good performance

#### Xeon Phi

- Xeon Phi hardware has potential for high peak performance

- Particularly at single precision

- Achievable performance generally lower

- Especially if memory or communication bound

- Full vectorisation and FMA essential for highest performance

- Can still get good performance without

- Good memory re-use essential for highest performance

- Same as for normal CPU code